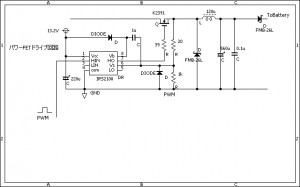

ダウン(電圧降下)コンバータのハイサイドスイッチは、ゲート電圧の制御のしやすさから、今までPchFETを使っていたが、ドライバICを入手したので、性能が良くて安価なNchFETに変えて動作検証をしている。

ドライバの出力は、立上がり立下がりがかちっとしていてさすがと思ったが、少々不可解な現象が確認された。

最初に入力電圧を掛けると、きちんとPWMパルスに応じてゲートドライブ端子(IRS2108の7ピンHO)にパルスが現れる。しかし、出力電圧が上がりすぎるなどして、一度PWMパルスが停止した後、再度PWMパルスを2ピンHINに入れてもHOにパルスが現れない。

チャージポンプ回路で高電圧を生成している原理は、Vs(6ピン)とVb(8ピン)の間のコンデンサをVsの電圧を13.2Vよりも下げた時に充電し、それをPWMパルスのタイミングに放電して高電圧を得るというもの。

オシロで現象を確認すると、PWMパルスが停止した後、Vs端子、つまりは、スイッチングのFETの出力側電圧は、高いままになっている。電流が流れていないんだから、インダクタの先にあるコンデンサに充電された電圧が現れているので、当り前。

つまり、PWMパルスが停止すると、Vs端子の電圧が下がらないため、コンデンサにチャージされず、パルスが再開しても、最初の一発のゲートパルスがキックできない現象と判明。

電流を逃がすためにVs端子に1kΩの抵抗をGNDとの間に追加してみた。

PWMが停止した後のVs端子の電圧を確認すると、抵抗を介してコンデンサの電荷が逃げていくので、ゆっくりと電圧が下がる。そこで、PWMパルスを再開させると、期待通りHO端子にパルスが現れるようになった。ただ、1kの抵抗を付けると言うことは、出力側で常に電流がリークしていると言うことで、なんだかもったいないような。。。しかも、電圧の下がり方は2~3秒かかるということで、その間にパルスが再開しても反応しない。抵抗値を下げれば早くなるのだけど、その分リーク電流も増えてしまう。今ひとつ良い解決策が思いつかない。

さらに、立上りが急峻なため、上がった瞬間に発振が起こり、出力にノイズとなって現れている。HOとFETのゲート間の抵抗値を増やせばノイズは小さくなるが、立上りがなまってしまう。なかなかに調整が難しい。

ドライバICは良くできていると思ったものの、うまく使うには、まだまだ勉強が必要そうだ。

PWMロジックは、出力電圧を測定してフィードバック制御掛けているが、パルスがゲートにかからないと、当然出力電圧が上がらず、PWM幅が足りないと判断して幅を拡げてしまう。で、広がったところでいきなりパルスが来ると、電圧が一気に下がりPWM停止してしまう。うまくいかないので、ロジックもいじらなければならない。

やってみて分るこういった細かい調整とロジック組込みの必要性です。奥深し。。。。