DCDCコン開発はまだまだ続く・・・・

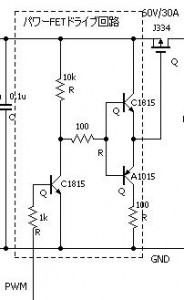

パワーFETのドライブが、典型的なプッシュ/プルと言うトランジスタドライブ回路で動くようになった。ただ、FALL時のなまりはもう少し。一気に電荷を抜く方法を工夫しないとならないようだ。

ところで、FETのソース/ゲート間電位差は20V以内に抑えなければならないが、単結晶の太陽光パネルの起電力は30V弱。NexPowerの薄膜系はより高く80Vにもなる。

この回路でドライブすると、ゲート電圧が起電力の間でスイングしてFETの絶対定格を超えFETが破壊されてしまう。

CPUを駆動するローサイドコモンの5Vから、FETゲートを駆動するのは意外と難しい。GNDを中間電位で取ると、AD変換の基準GNDが浮いてしまい電圧測定誤差が大きくなる。

何か良い方法はないか。まだまだ勉強不足で良い解決方法が思い浮かばない。

プログラムは完成度が上がって、パラメータの調整段階に到達し、保護ロジックなどを組込み始めた。異常時には安全側に制御するため、電圧、電流の上限値を超えたら緊急停止させている。

しかし、電源ON直後は、コンデンサを充電する突入電流が瞬間的に流れる。電圧、電流測定ループを割込み制御に変えたため、非常にクリティカルに検知可能となった結果、瞬時値で異常検知し緊急停止するので先に進まなくなってしまった。過渡的な挙動を考慮し、その場合は回避するロジックを作らなねばならないか。。。

面倒くさ・・・・などと言っては罰が当る。実際に作ってみて分る貴重なノウハウと考えなければ。。。。日々これ勉強。。。。肝に銘じておこう。

なんて、悠長なことを言っているが、すでにPICのプログラム書込み領域は84%も使ってしまったため、複雑な処理は追加できない。。。。悩ましい問題だ。

(プロ) トリッキーな回路で分圧する手もあるかもしれませんが、大きな電流を扱うため、誤動作が許されない、また測定、シミュレーションといった環境が厳しい自作であることから、素直に耐圧の高いFETを選択されては如何でしょうか。速度は遅くなり効率は落ちますが、SW周波数が低いのでさほど劣化はしないのではないでしょうか。

もしこだわるのであれば、金に糸目をつけずに、SiCを使えば耐圧1KV超えでも速度はビンビンです。

蛇足ですが、回路の設計を楽しむ自作派には邪道かもしれませんが、ロジック系の回路とのインタフェースはFETドライバーを使えば簡単です。

(私) 電位が異なっていても制御出来るようにフォトカプラを使おうかと思っているのですが、40kHzぐらいの速度だったら特に問題なく動いてくれるのでしょうかねぇ。ただ、フォトカプラは時間と共に劣化で光量が落ちるとも聞くので。。FETドライバも調べてみます。

SiCは、まだまだなかなか入手が厳しいですし高価ですからね。IRの代理店をやっている会社とお仕事で色々とお付き合いしているので、GaNなら手に入るかも。。。とか思っていますが、趣味の範囲を超えちゃいますからね。

(プロ) ご存知の通り、フォトカプラは発光部分が寿命を持ちますからいつかは必ず壊れます。データシートには出荷時の特性で、劣化分は加味されていません。実は寿命に関するベンダーの推定値はばらばらで、倍半分どころか数倍もオーダーが異なります。加速試験の手法がしっかり確立していないのでしょう。

一般的にはGaAlAs系は寿命が短いことになっていますが、フィールド実績でみると、それよりベンダー依存性が強い傾向があります。X社を除く国産品をちゃんとした設計で使えば大丈夫だと思います。設計上の要点は、必ず寿命を加味して劣化しても動作するようにすること、但しマージンを大きく採ろうとして明るく光らせ過ぎると返って寿命を縮めます。温度に対する配慮も大切で、発熱部品には実装位置を近づけないことも大切です。

40KHzのSW周波数というのは、フォトカプラに普通のFETではかなり厳しいですね。ここを頑張っているのは、制御性の問題でしょうか?こっちはあまり詳しくないのですが、例えばフィードフォワード項を入れるといった制御を入れて、もっとSW周波数を落とすことを考えてみるのも良いのかもしれません。

(私) フォトカプラはやはりそうですか。40kと言うのは、80円のPICで限界はどこまで?ってな感じでとりあえず定めたものなので、あまり意味はありません。周波数を上げるとLCが小さくなる効果はあります。安価で容易に入手できるインダクタに合わせてという意味はありますが、20kくらいでも大丈夫そうです。

2SA1015の下の抵抗を1015の直上に持っていって、1kΩにすると、適度になまって、ゲート電圧をあまり下げずに済むことが確認できたので、ここをうまく制御してあげれば、ゲート電圧を許容範囲に抑えられそうです。さらに、スイッチングONの瞬間に、アウトプットにノイズが乗ってしまうのは、A1015の上のC1815の直上に100Ωの抵抗をはさむことによって抑えられました。その他、抵抗値を増やしても問題なさそうなところを調整して消費電流を削減しました。オシロで波形を確認しながら、抵抗の値や位置によって微妙に変るのは、良い勉強になります。