理論的には動作する設定で動かないという現象が出ており、その理由を解析中。

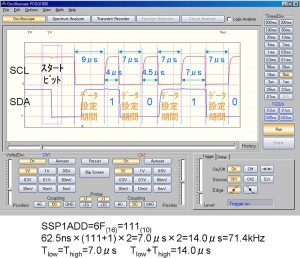

先ずは、実際の動作状況をオシロで確認してみた。I2C信号線、SCL(クロック)とSDA(データ)を見てみると、図のような波形が観測された。ただし、これは、たまに発生するもので、ほとんどは、SCLのHigh期間は概ね7μsという図の右寄りのクロック幅のもの。観測していると、数秒に1度、クロックのHigh幅が短いものが発生する。

プログラム上の設定では、上記のようにbaudレートジェネレータに6Fを設定しているので、SCLがHigh(Thigh)もLow(Tlow)も概ね7μsとなるはずなのに、たまに設定よりも短い4μsという時間でトリガがかかっているようだ。PICのデータシートには、そのような記載はないようなので、理由は不明。

では、この症状で、理論的には可能と思われる88(10)で動作しない現状は説明できるか検証してみる。

今回の現象は、baudレートジェネレータのタイマが、7μsを計測するべきところが、たまに4μsという短いタイマでトリガをかけてしまっていると言うこと。では、SSP1ADD=88と設定が7μsよりも短い5.5μsの設定の時にはどうなるか。7と4の関係が半分ではなく、微妙なところが現象の予測は難しいが、5.5×(4/7)=3.1μsとしてみよう。

LCDの仕様では、Thighは2.4μs以上となっているので、これは満たしているようだ。よって、この現象も今回の症状を説明するに足るものではなさそうだ。

なかなか難しい解析である。