・PICのbaudレートジェネレータ

特に動作タイミングを規定するうえで重要なのは、PICのMSSPモジュールのbaudレートジェネレータである。baudレートジェネレータとは、データ交換するタイミングを生成するクロックと考えてよい。ただ、単純なクロック生成器ではなく、動作を行う前に一定時間の遅延を生成する機構と考えればよい。baudレートジェネレータの持つタイマに設定された値をカウントダウンし、0になった時にトリガが生成される。

タイマの初期値を設定しておくのがSSP1ADDレジスタである。このレジスタは、スレーブモードで動作するときは、デバイス自体のスレーブアドレスを設定するためにこんな名称になっており、わかりづらい。マスタモードでは自身のスレーブアドレスは保存する必要がないため、全く別のbaudレートジェネレータ用途に使われているということ。

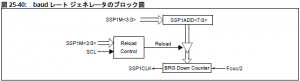

図25-40にあるように、baudレートジェネレータには、Fosc/2のクロックが供給されている。PICのFoscとは、PICの動作タイミングを生成するクロック信号である。PICは、クロック4つで1セットとして動作するように設計されている。便宜的に、FoscクロックにQ1、Q2、Q3、Q4、Q1、Q2・・・・と名称を付けている。baudレートジェネレータには、Q2とQ4にタイミングでクロックが供給される。

例えば、PIC16F1823を内部クロック最高の32MHzで動作させる場合を考える。Foscは32MHzとなる。よって、baudレートジェネレータには16MHzのクロック(62.5ns)が供給される。1クロックでタイマがデクリメントされるため、10が設定されているとトリガ発生までに62.5×10=625nsの遅延が生じる。実際には、SSP1ADDレジスタからタイマに初期設定するために1クロックかかるため11クロック(687.5ns)の遅延トリガがかかることとなる。つまり、タイマ遅延は(SSP1ADD+1)×Focs/2となる。

表25-4を検証してみよう。32MHzの場合に100kHzのI2Cクロックを生成する場合のSSP1ADDの値(タイマ初期値)は16進数4Fとなっている。10進数では79である。この場合のタイマ遅延は、(SSP1ADD+1)×Focs/2=80×62.5ns=5μsとなる。100kHz=10μsで、Low期間とHigh期間の合計だから、baudレートジェネレータは5μs毎のトリガでSCLラインのLowとHighを切り替えるために使われることが理解できる。

・スルーレート制御

SSP1STAT(SSP1ステータスレジスタ)にビット7にSMPというフラグがある。説明には以下の記述があるが、何のことかさっぱりわからない。

I2Cマスタまたはスレーブモード:

1 = スルーレート制御の標準速度モード(100 kHz と1 MHz) を無効に設定する

0 = スルーレート制御の高速モード(400 kHz) を有効にする

せめて以下のように日本語として理解できる程度に翻訳してほしい。

1= 標準速度モード(100kHz および1MHz)、スルーレート制御は行わない

0= 高速モード(400kHz)、スルーレート制御を行う

さて、スルーレート制御とは、何ぞや。

スルーレートというのは、電圧が変化するスピードで、素人目には速いほどよいように思える。しかし、早くしすぎると、リンギング(オーバーシュート、アンダーシュート)などで波形が乱れるばかりでなっく、下手すると、高電圧でデバイスを壊しかねない。スルーレートをコントロールすることでリンギングを減少させ、結果として信号が安定するまでの時間を短くすることができる。これによって、高速モード(400kHz)で通信が可能となる。

よいことづくめなので、デフォルト有効にすべきと思うのだが、立上り下りの条件が変わるので、過去の回路との互換性を配慮してのことなのか。

・タイミングチャート

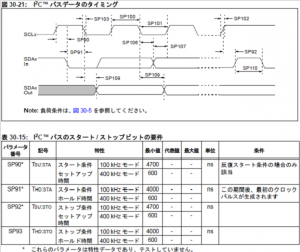

データシートの巻末にタイミングチャートがある。I2Cについてもあるので、確認しておく。

SMPフラグの違いが顕著にわかる。スタートアップ設定時間が、スルーレートオフ(100kモード)では4.7μsなのに、オン(400kモード)では0.6μsと、はるかに小さくなっている。あらゆる動作でスルーレート制御の効果が確認できる。

ただ、遅いデバイスが、この早さに付いてこられるかは、確認しなければならないことは、言うまでもない。