負荷用電源の効率アップをする方法について検討する。

ポイントは以下の通り。

- タイマーIC555の発振からトランジスタをドライブする際、抵抗で波形がなまるところをスピードアップコンデンサを抵抗と並行に設置し高速化

- FETドライブ回路をプッシュプル型にしてゲートへのチャージ、ディスチャージを高速化

- FET保護のためスナバ回路の追加

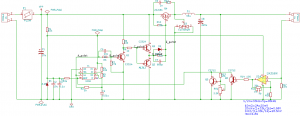

改良型回路図は以下の通り。

定数は、実際にテストしながら最終決定をしようと思う。

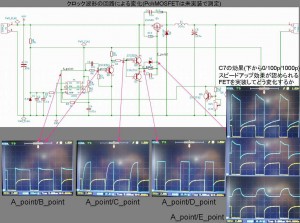

回路の主要点で波形を確認した結果を以下に示す。

なかなか面白い結果だ。上記のオシロ波形は、ゲートドライブにFETを未接続で行っているため、電流がちょっと流れると電圧がぽんと飛び上がる現象が確認できる。

A_pointは555の出力で、少しなまっている。B_pointはスピードアップコンデンサのおかげで、矩形波になっている。コンデンサが少々大きすぎるためか、オーバーシュート気味だが、問題になるほどではない。C_pointでは、なまってしまっているが、プッシュプルのおかげでD_pointはみごとな矩形波。これは素晴らしい。

そして、問題のゲートドライブ部分のE_point。テストでは、D2は未実装。

コンデンサがない状態では、15k、39kΩという大きな抵抗のおかげでみごとになまっており、このままでは、効率アップは望むべくも無い。

D2は、ゲートチャージを高速化するときのテクニックとしてよく見かけるが、今回の回路ではゲート電荷を引き抜くときには役に立たない。そこで、スピードアップコンデンサをここにも挿入してみる。容量はどの程度が適切なのか。

100pFで調べると、効果覿面。だが、オーバーシュートしている。さらに1000pFでは、大きくオーバーシュートしている。ここで、注意しなければならないのが、GS間の耐圧だ。一般にパワーFETは20Vであり、これを超えたら破壊してしまう。

ただ、この様子は、FETを接続していないため、電子の行き場が無く大きく電圧が上昇していると想定される。では、FETのゲートを接続したらどうか。

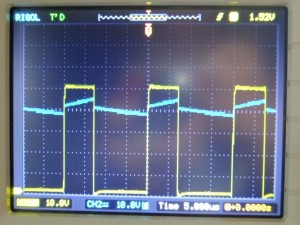

100pFの場合 1000pFの場合

100pFでは電荷が足りずに十分ゲート電圧が戻せていないため、ゲートが開きっぱなしになってしまいそうだ。一方、1000pFではオーバーシュートしている。GS間の耐圧を超えてしまうことが少々不安だ。

スイッチングに利用しているFETは、2SJ681。このデータシートを紐解くと、入力容量Ciss=700pF、出力容量Coss=90pFとある。これが肝。スピードアップコンデンサの容量は、Cissに整合させてやることで、必要最小限のチャージ電荷を高速に供給することができるという訳。大きすぎると、余分な電荷が電圧上昇を招き、下手するとFETを破壊する。

そこで、680pFにコンデンサを付け替えて試してみるとはたして。。。。

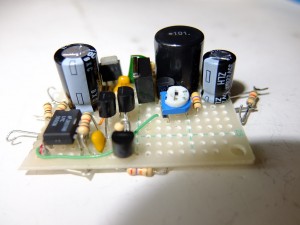

みごとにドンピシャ。負荷用電源DCDCコンバータ改良型のテスト基板はこんな感じ。電流制限のためのOPアンプ回路はまだ未実装。

回路の改善によって、FETの発熱がほぼ無くなった。350mA程度なら、FETは常温と変わらないレベル。これなら、基板上の表裏のパタンだけによる放熱でもある程度は大丈夫そう。

ゲートパルスを矩形波に近づけるだけで、ここまで劇的に効果が出るのは気持ちいい。発熱がないと言うことは、無駄な電力消費がないことだから効率が良いと言うこと。発熱が少ないと、部品の寿命も延びるため、良いことづくめ。回路のチューニングはとても重要だ。